# TG7121B 硬件设计指导

芯片开放社区

Open Chip Community

---

## 版本记录

|      |         |            |               |

|------|---------|------------|---------------|

| V1.0 | Xianwei | 2019.10.13 | 初版            |

| V1.1 | Xianwei | 2020.01.14 | 更新 BOM 表、参考电路 |

| V2.0 | Xianwei | 2020.11.08 | 更改芯片尺寸、新增电气说明 |

| V2.1 | Xianwei | 2020.12.08 | 增加 pcb 画制注意事项 |

---

## 目录

|                       |           |

|-----------------------|-----------|

| 第一章：芯片简介 .....        | 4         |

| 1.1：功能介绍.....         | 4         |

| 1.2：引脚定义图 .....       | 4         |

| 第二章：参考系统设计 .....      | 4         |

| 2.1 量产系统 .....        | 错误!未定义书签。 |

| 2.1.1：量产系统原理图(1)..... | 5         |

| 2.1.2：量产系统原理图(2)..... | 错误!未定义书签。 |

| 第三章：PCB 画制注意事项 .....  | 6         |

| 第四章：外形尺寸和电气参数 .....   | 7         |

# 第一章：芯片简介

## 1.1：功能介绍

TG7121B 是天猫精灵针面向小家电智能化推出的蓝牙 Mesh 芯片，具有极简的电路设计，优异的射频性能，工业级温宽范围(-40°C~85°C)及易生产的 SOP16 封装等特点。

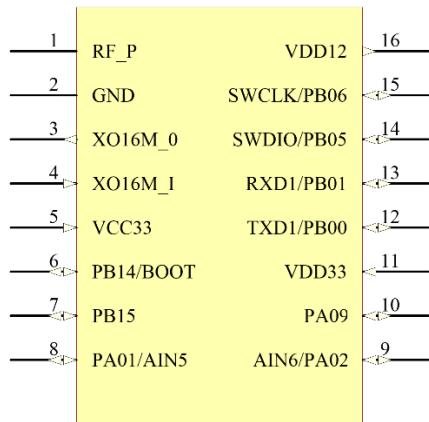

## 1.2：引脚定义图

图 1、SOP16 器件图

GPIO 具有全功能映射。

引脚定义：

| NO | Pin Name | Remark            |

|----|----------|-------------------|

| 1  | RF_P     | 射频引脚              |

| 2  | GND      | 芯片地               |

| 3  | XO16M_O  | 16M 晶振输出          |

| 4  | XO16M_I  | 16M 晶振输入          |

| 5  | VCC33    | 芯片 3.3V 输入        |

| 6  | PB14     | GPIO/BOOT 控制      |

| 7  | PB15     | GPIO/休眠唤醒         |

| 8  | PA01     | GPIO/ADC 通道 5     |

| 9  | PA02     | GPIO/ADC 通道 6     |

| 10 | PA09     | GPIO              |

| 11 | VDD33    | 芯片 3.3V 电源        |

| 12 | PB00     | GPIO/UART1_TXD    |

| 13 | PB01     | GPIO/UART1_RXD    |

| 14 | PB05     | GPIO(调试口数据接口)     |

| 15 | PB06     | GPIO(调试口时钟接口)     |

| 16 | VDD12    | 芯片 1.2V 电源 (无需外接) |

## 第二章：参考系统设计

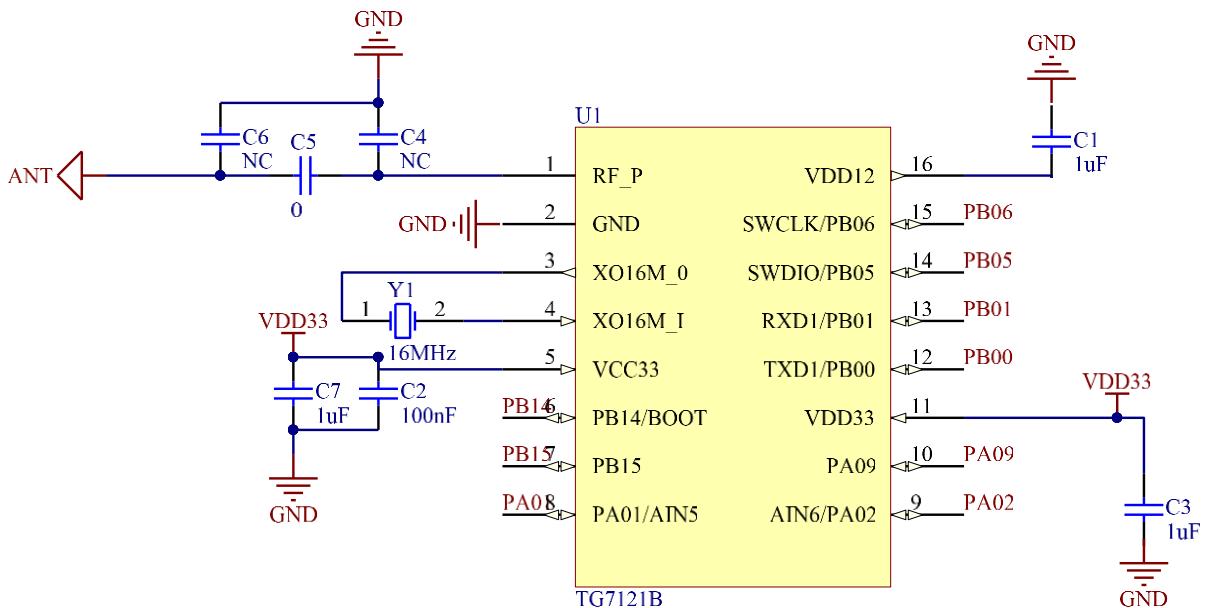

2.1.1：量产系统原理图

图 2：参考系统

注：

- 1、NRST 为复位引脚，低电平复位

- 2、PB00 和 PB01 上电后默认为 UART1 的 TX、RX 接口，可在程序中更改功能

- 3、在使用 UART 烧录时，需要将 PB14 置为高电平，再上电。

- 4、若使用时，TX 功率在 10dBm 以上，需要在 VDD\_PAHP(PIN23) 外围加一个 1uF 的电容

- 5、芯片的 PIN5(VCC33) 和 PIN11(VDD33) 都是电源输入引脚。VDD12 为电源引脚，只需要外挂电容。

表一：量产系统 BOM 表

| 序号 | 器件      | 物料规格             | 位号       | 数量 |

|----|---------|------------------|----------|----|

| 1  | TG7121B | SOP16            | U1       | 1  |

| 2  | 晶振      | 16MHZ ±10PPM 9F  | Y1       | 1  |

| 3  | 贴片电容    | (±10%)/10V/100nF | C2       | 1  |

| 4  | 贴片电容    | (±10%)/10V/1uF   | C1、C3、C7 | 3  |

---

# 第三章：PCB 画制注意事项

## 3.1 阻抗

天线可以看做是一个谐振回路。一个谐振回路当然有其阻抗。我们对阻抗的要求就是匹配：和天线相连的电路必须有与天线一样的阻抗。和天线相连的是馈线，馈线的阻抗是确定的，所以我们希望天线的阻抗和馈线一样 50 欧姆。

## 3.2 如何选择天线

选择天线类型的意义是：所选天线的方向图是否符合系统设计中电波覆盖的要求；选择天线电气性能的要求是：选择天线的频率带宽、增益、尺寸、额定功率等电气指标是否符合系统设计要求。

这里特别说下尺寸，尺寸是一个很重要的天线特性，天线需要控制和移动就限制了天线的实际尺寸大小，需要在屏蔽室内使用天线也限制了天线的最大尺寸，需要减小对地或对周围物体不希望有的耦合也将影响尺寸，但相反地，希望天线有好的低频响应，增益高或带宽宽，就要增大天线的尺寸。

## 3.3 走线

直角走线一般是 PCB 布线中要求尽量避免的情况，也几乎成为衡量布线好坏的标准之一。那么直角走线究竟会对信号传输产生多大的影响呢？从原理上说，直角走线会使传输线的线宽发生变化，造成阻抗的不连续。其实不光是直角走线，顿角，锐角走线都可能会造成阻抗变化的情况。

影响就是主要体现在三个方面：一是拐角可以等效为传输线上的容性负载，减缓上升时间；二是阻抗不连续会造成信号的反射；三是直角尖端产生的 EMI。、

## 3.4 串扰

(1) 串扰表现为在一根信号线上有信号通过时，在 PCB 板上与之相邻的信号线上就会感应出相关的信号，我们称之为串扰。

(2) 信号线距离地线越近，线间距越大，产生的串扰信号越小。异步信号和时钟信号更容易产生串扰。因此解串扰的方法是移开发生串扰的信号或屏蔽被严重干扰的信号。

## 3.5 布局

元件在印刷线路板上排列的位置要充分考虑抗电磁干扰问题，原则之一是各部件之间的引线要尽量短。在布局上，要把模拟信号部分、高速数字电路部分、噪声源部分，这三部分合理地分开，使相互间的信号耦合为最小。对噪声和干扰非常敏感的电路或高频噪声特别严重的电路应该用金属罩屏蔽起来。

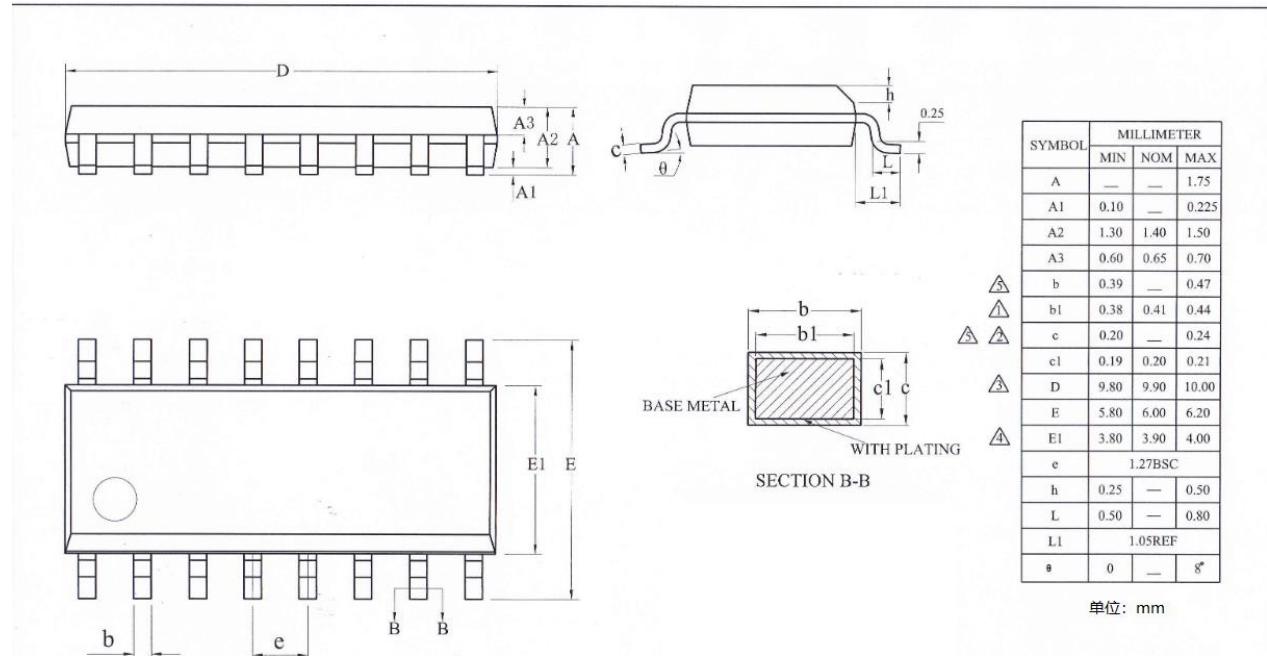

# 第四章：外形尺寸和电气参数

外形尺寸：

图：TG7121B 外形尺寸 (SOP16)

电气特性：

| Parameter             | Description                     | Min.    | Typ.  | Max.    | Unit |

|-----------------------|---------------------------------|---------|-------|---------|------|

| Operating Temperature |                                 | -40     |       | 105     | °C   |

| Supply Voltage        | Regulator supply input          | 1.8     | 3.3   | 3.6     | V    |

| Current Consumption   | TX Mode @ 0dBm Output (DCDC ON) |         | 4.3   |         | m A  |

|                       | RX Mode (DCDC ON)               |         | 4.5   |         | m A  |

|                       | Standby Mode                    |         | 2     |         | m A  |

|                       | Low Power Mode2                 |         | 1.1   |         | u A  |

|                       | Low Power Mode3                 |         | 0.7   |         | u A  |

|                       |                                 |         |       |         |      |

| VIH                   | High Level Input Voltage        | 0.9*VDD |       | VDD     | V    |

| VIL                   | Low Level Input Voltage         | 0       |       | 0.1*VDD | V    |

| VOH                   | High Level Output Voltage       | VDD-0.4 |       | VDD     | V    |

| Source Current        |                                 |         | 60    |         | m A  |

| VOI                   | Low Level Output Voltage        | 0       |       | 0.4     | V    |

| Sink Current          |                                 |         | 30    |         | m A  |

| VESD                  | Electrostatic discharge voltage |         | ±8000 |         | V    |

| Vmm                   |                                 |         | ±400  |         | V    |

| VLP                   |                                 |         | ±400  |         | m A  |